# **GPIB**

## TNT5002™ Technical Reference Manual

PCI to GPIB High-Performance Non-Controller

#### **Worldwide Technical Support and Product Information**

ni.com

#### **National Instruments Corporate Headquarters**

11500 North Mopac Expressway Austin, Texas 78759-3504 USA Tel: 512 683 0100

#### **Worldwide Offices**

Australia 61 2 9672 8846, Austria 43 0 662 45 79 90 0, Belgium 32 0 2 757 00 20, Brazil 55 11 3262 3599, Canada (Calgary) 403 274 9391, Canada (Montreal) 514 288 5722, Canada (Ottawa) 613 233 5949, Canada (Québec) 514 694 8521, Canada (Toronto) 905 785 0085, Canada (Vancouver) 514 685 7530, China 86 21 6555 7838, Czech Republic 42 02 2423 5774, Denmark 45 45 76 26 00, Finland 385 0 9 725 725 11, France 33 0 1 48 14 24 24, Germany 49 0 89 741 31 30, Greece 30 2 10 42 96 427, Hong Kong 2645 3186, India 91 80 4190000, Israel 972 0 3 6393737, Italy 39 02 413091, Japan 81 3 5472 2970, Korea 82 02 3451 3400, Malaysia 603 9059 6711, Mexico 001 800 010 0793, Netherlands 31 0 348 433 466, New Zealand 64 09 914 0488, Norway 47 0 32 27 73 00, Poland 48 0 22 3390 150, Portugal 351 210 311 210, Russia 7 095 238 7139, Singapore 65 6 226 5886, Slovenia 386 3 425 4200, South Africa 27 0 11 805 8197, Spain 34 91 640 0085, Sweden 46 0 8 587 895 00, Switzerland 41 56 200 51 51, Taiwan 886 2 2528 7227, United Kingdom 44 0 1635 523545

For further support information, see the *Technical Support and Professional Services* appendix. To comment on the documentation, send email to techpubs@ni.com.

© 2003 National Instruments Corporation. All rights reserved.

# **Important Information**

#### Warranty

The TNT5002 is warranted against defects in materials and workmanship for a period of one year from the date of shipment, as evidenced by receipts or other documentation. National Instruments will, at its option, repair or replace equipment that proves to be defective during the warranty period. This warranty includes parts and labor.

The media on which you receive National Instruments software are warranted not to fail to execute programming instructions, due to defects in materials and workmanship, for a period of 90 days from date of shipment, as evidenced by receipts or other documentation. National Instruments will, at its option, repair or replace software media that do not execute programming instructions if National Instruments receives notice of such defects during the warranty period. National Instruments does not warrant that the operation of the software shall be uninterrupted or error free.

A Return Material Authorization (RMA) number must be obtained from the factory and clearly marked on the outside of the package before any equipment will be accepted for warranty work. National Instruments will pay the shipping costs of returning to the owner parts which are covered by warranty.

National Instruments believes that the information in this document is accurate. The document has been carefully reviewed for technical accuracy. In the event that technical or typographical errors exist, National Instruments reserves the right to make changes to subsequent editions of this document without prior notice to holders of this edition. The reader should consult National Instruments if errors are suspected. In no event shall National Instruments be liable for any damages arising out of or related to this document or the information contained in it.

Except as specified herein, National Instruments makes no warranties, express or implied, and specifically disclaims any warranty of merchantability or fitness for a particular purpose. Customer's right to recover damages caused by fault or negligence on the part of National Instruments shall be limited to the amount therefore paid by the customer. National Instruments will not be liable for Damages resulting from loss of data, profits, use of products, or incidental or consequential damages, even if advised of the possibility thereof. This limitation of the liability of National Instruments will apply regardless of the form of action, whether in contract or tort, including negligence. Any action against National Instruments must be brought within one year after the cause of action accrues. National Instruments shall not be liable for any delay in performance due to causes beyond its reasonable control. The warranty provided herein does not cover damages, defects, malfunctions, or service failures caused by owner's failure to follow the National Instruments installation, operation, or maintenance instructions; owner's modification of the product; owner's abuse, misuse, or negligent acts; and power failure or surges, fire, flood, accident, actions of third parties, or other events outside reasonable control.

#### Copyright

Under the copyright laws, this publication may not be reproduced or transmitted in any form, electronic or mechanical, including photocopying, recording, storing in an information retrieval system, or translating, in whole or in part, without the prior written consent of National Instruments Corporation.

#### **Trademarks**

$HS488^{\text{TM}}$ , National Instruments M, NIM, ni.com NI-488.2 M, NI-488DDK NI-488DDK TNT4882 M, TNT488C M, and TNT5002 are trademarks of National Instruments Corporation.

Product and company names mentioned herein are trademarks or trade names of their respective companies.

#### **Patents**

For patents covering National Instruments products, refer to the appropriate location: **Help»Patents** in your software, the patents.txt file on your CD, or ni.com/patents.

#### WARNING REGARDING USE OF NATIONAL INSTRUMENTS PRODUCTS

(1) NATIONAL INSTRUMENTS PRODUCTS ARE NOT DESIGNED WITH COMPONENTS AND TESTING FOR A LEVEL OF RELIABILITY SUITABLE FOR USE IN OR IN CONNECTION WITH SURGICAL IMPLANTS OR AS CRITICAL COMPONENTS IN ANY LIFE SUPPORT SYSTEMS WHOSE FAILURE TO PERFORM CAN REASONABLY BE EXPECTED TO CAUSE SIGNIFICANT INJURY TO A HUMAN.

(2) IN ANY APPLICATION, INCLUDING THE ABOVE, RELIABILITY OF OPERATION OF THE SOFTWARE PRODUCTS CAN BE IMPAIRED BY ADVERSE FACTORS, INCLUDING BUT NOT LIMITED TO FLUCTUATIONS IN ELECTRICAL POWER SUPPLY, COMPUTER HARDWARE MALFUNCTIONS, COMPUTER OPERATING SYSTEM SOFTWARE FITNESS, FITNESS OF COMPILERS AND DEVELOPMENT SOFTWARE USED TO DEVELOP AN APPLICATION, INSTALLATION ERRORS, SOFTWARE AND HARDWARE COMPATIBILITY PROBLEMS, MALFUNCTIONS OR FAILURES OF ELECTRONIC MONITORING OR CONTROL DEVICES, TRANSIENT FAILURES OF ELECTRONIC SYSTEMS (HARDWARE AND/OR SOFTWARE), UNANTICIPATED USES OR MISUSES, OR ERRORS ON THE PART OF THE USER OR APPLICATIONS DESIGNER (ADVERSE FACTORS SUCH AS THESE ARE HEREAFTER COLLECTIVELY TERMED "SYSTEM FAILURES"). ANY APPLICATION WHERE A SYSTEM FAILURE WOULD CREATE A RISK OF HARM TO PROPERTY OR PERSONS (INCLUDING THE RISK OF BODILY INJURY AND DEATH) SHOULD NOT BE RELIANT SOLELY UPON ONE FORM OF ELECTRONIC SYSTEM DUE TO THE RISK OF SYSTEM FAILURE. TO AVOID DAMAGE, INJURY, OR DEATH, THE USER OR APPLICATION DESIGNER MUST TAKE REASONABLY PRUDENT STEPS TO PROTECT AGAINST SYSTEM FAILURES, INCLUDING BUT NOT LIMITED TO BACK-UP OR SHUT DOWN MECHANISMS. BECAUSE EACH END-USER SYSTEM IS CUSTOMIZED AND DIFFERS FROM NATIONAL INSTRUMENTS' TESTING PLATFORMS AND BECAUSE A USER OR APPLICATION DESIGNER MAY USE NATIONAL INSTRUMENTS PRODUCTS IN COMBINATION WITH OTHER PRODUCTS IN A MANNER NOT EVALUATED OR CONTEMPLATED BY NATIONAL INSTRUMENTS, THE USER OR APPLICATION DESIGNER IS ULTIMATELY RESPONSIBLE FOR VERIFYING AND VALIDATING THE SUITABILITY OF NATIONAL INSTRUMENTS PRODUCTS WHENEVER NATIONAL INSTRUMENTS PRODUCTS ARE INCORPORATED IN A SYSTEM OR APPLICATION, INCLUDING, WITHOUT LIMITATION, THE APPROPRIATE DESIGN, PROCESS AND SAFETY LEVEL OF SUCH SYSTEM OR APPLICATION.

# **Contents**

| Aboı | ut This Manual                       |     |

|------|--------------------------------------|-----|

|      | Product Features                     | xi  |

|      | How To Use This Manual               |     |

|      | Conventions                          |     |

|      | Mnemonic Conventions                 | xiv |

|      | Related Documentation                | xv  |

| Cha  | pter 1                               |     |

| _    | nitectural Overview                  |     |

|      | TNT5002 Block Diagram                | 1-1 |

|      | TNT5002 Mode Selection               |     |

|      | FIFO Overview                        | 1-2 |

|      | DMA Overview                         | 1-3 |

| Chai | pter 2                               |     |

| -    | ial Pins                             |     |

|      | Signal Definitions and Conventions   | 2-1 |

|      | GPIB Signals                         |     |

|      | GPIB Data Signals                    | 2-2 |

|      | GPIB Interface Management Signals    | 2-2 |

|      | GPIB Handshake Signals               |     |

|      | Device Signals                       |     |

|      | Miscellaneous Signals (All Modes)    |     |

|      | Miscellaneous Signals (PCI4882 Mode) |     |

|      | Indicator Signals                    |     |

|      | PCI Signals                          |     |

|      | Generic Interface Signals            |     |

|      | Power/Ground Pins                    |     |

|      | PCI4882 Power/Ground Pins            |     |

|      | GEN4882 Power/Ground Pins            | 2-9 |

| Cha  | pter 3                               |     |

| Regi | ister Descriptions                   |     |

|      | Register Groups                      | 3-1 |

|      | Register Groups in PCI4882 Mode      |     |

|      | Register Groups in GEN4882 Mode      | 3-2 |

|      | PCI4882 Mode Register Map            | 3-2 |

| (                  | iEN4882 Mode Register Map                           | 3-4  |

|--------------------|-----------------------------------------------------|------|

| Т                  | NT5002 Status/Control Register Group                | 3-5  |

|                    | TNT5002 Status/Control Registers Sorted by Offset   | 3-5  |

|                    | TNT5002 Status/Control Registers Sorted by Mnemonic |      |

|                    | TNT5002 Status/Control Register Descriptions        |      |

| F                  | CI Configuration Registers                          |      |

|                    | PCI Configuration Register Map                      |      |

|                    | PCI Configuration Register Descriptions             |      |

| Ι                  | DMA Status/Control Registers                        |      |

|                    | DMA Status/Control Registers Sorted by Offset       |      |

|                    | DMA Status/Control Registers Sorted by Mnemonic     |      |

|                    | DMA Status/Control Register Descriptions            |      |

| 4                  | 882 Register Set                                    |      |

|                    | 4882-Mode Registers Sorted by Offset                |      |

|                    | 4882-Mode Registers Sorted by Mnemonic              |      |

|                    | 4882-Mode Register Descriptions                     |      |

| S                  | erial Number Register                               |      |

| Chapte<br>Function | r 4<br>nal Description—PCI4882 and GEN4882 Modes    |      |

| (                  | Overview                                            | 4-1  |

| (                  | GPIB Reset Manager                                  | 4-2  |

|                    | Overview                                            |      |

|                    | Hardware Resets                                     | 4-2  |

|                    | Register Bit Description                            |      |

|                    | Operation                                           |      |

| 7                  | 'alker/Listener Manager                             |      |

|                    | Overview                                            | 4-6  |

|                    | Register Bit Definitions                            |      |

|                    | Operation                                           |      |

| (                  | GPIB Transfer Manager                               |      |

|                    | Overview                                            | 4-11 |

|                    | Initialization Phase—Register Bit Definitions       | 4-12 |

|                    | Initialization Phase—Operation                      | 4-21 |

|                    | Data Transfer Phase—Register Bit Definitions        |      |

|                    | Data Transfer Phase—Operation                       |      |

|                    | Termination Phase—Register Bit Definitions          |      |

|                    | Termination Phase—Operation                         |      |

|                    | Using 8-bit FIFOs                                   |      |

| Ι                  | Device Clear Block                                  |      |

|                    | Overview                                            | 4-30 |

|                    | Register Bit Definitions                            | 4-30 |

|                    | Operation                                           | 4-31 |

| Device Trigger Block                    | 4-33 |

|-----------------------------------------|------|

| Overview                                | 4-33 |

| Register Bit Definitions                | 4-33 |

| Operation                               | 4-35 |

| Serial Poll Response Manager            | 4-36 |

| Overview                                | 4-36 |

| Register Bit Definitions                | 4-36 |

| Operation                               | 4-39 |

| Parallel Poll Response Manager          | 4-42 |

| Overview                                | 4-42 |

| Register Bit Definitions                | 4-42 |

| Operation                               | 4-44 |

| Remote Local Block                      | 4-46 |

| Overview                                | 4-46 |

| Register Bit Definitions                | 4-46 |

| Operation                               | 4-48 |

| HS488 Manager                           | 4-49 |

| Overview                                | 4-49 |

| Register Bit Description                | 4-49 |

| Operation                               | 4-57 |

| Timer                                   | 4-59 |

| Overview                                | 4-59 |

| Register Bit Definitions                | 4-59 |

| Operation                               | 4-61 |

| Interrupts                              | 4-63 |

| Overview                                | 4-63 |

| Register Bit Descriptions               | 4-63 |

| Operation                               | 4-65 |

| Debugging Bits                          | 4-66 |

| Overview                                | 4-66 |

| Register Bit Descriptions               | 4-66 |

| Miscellaneous Bits                      | 4-76 |

| Overview                                | 4-76 |

| Rarely Used GPIB Transfer Bits          | 4-76 |

| Rarely Used Controller Bits             | 4-78 |

| Rarely Used Interrupt Bits              | 4-79 |

| Rarely Used Addressing Mode Bits        | 4-81 |

| Register Bit Definitions                | 4-81 |

| Operation—Extended Dual Addressing Mode | 4-83 |

| Chap           | ter 5                                   |       |

|----------------|-----------------------------------------|-------|

| -              | Manager                                 |       |

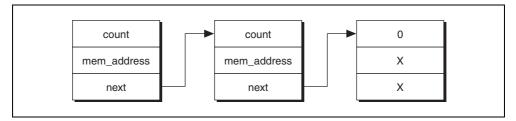

| <b>D</b> 11111 | DMA Overview                            | 5-    |

|                | Link Chaining Overview                  |       |

|                | DMA Transfers                           |       |

|                | Initialization Phase                    |       |

|                | Transfer Phase                          |       |

|                | Termination Phase                       |       |

|                | Alignment of Data in the DFIFO          | 5-5   |

| Chap           | ter 6                                   |       |

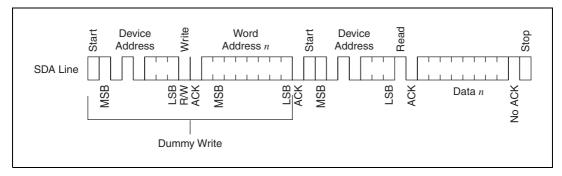

| -              | I ROM                                   |       |

|                | Overview                                | . 6-  |

|                | Serial Autoload                         | 6-    |

|                | Serial ROM Contents                     | . 6-  |

|                | PCI Device ID                           | . 6-2 |

|                | Serial Number                           | . 6-2 |

|                | Remaining Bytes                         |       |

|                | Accessing the EEPROM                    |       |

|                | Register Bit Descriptions               | 6-3   |

| Chap           | ter 7                                   |       |

| Clock          | <b>(S</b>                               |       |

|                | Clock Domains                           | 7-    |

|                | PCI4882 Mode                            | . 7-  |

|                | GEN4882 Mode                            | . 7-  |

| Chap           | ter 8                                   |       |

| Rese           | t Considerations                        |       |

|                | Hardware Resets                         | 8-    |

|                | PCI Reset (PCI4882 Mode Only)           |       |

|                | Generic Reset (GEN4882 Mode Only)       |       |

|                | Software Resets                         | 8-2   |

|                | GPIB Software Reset (PCI4882 Mode Only) | 8-2   |

|                | GPIB Hardware Reset (PCI_4882 Mode)     | . 8-2 |

|                | GPIB pon (All Modes)                    |       |

|                | GPIB Reset (All Modes)                  |       |

|                | DMA Reset (PCI4882 Mode)                |       |

|                | Power on Considerations                 | Q 1   |

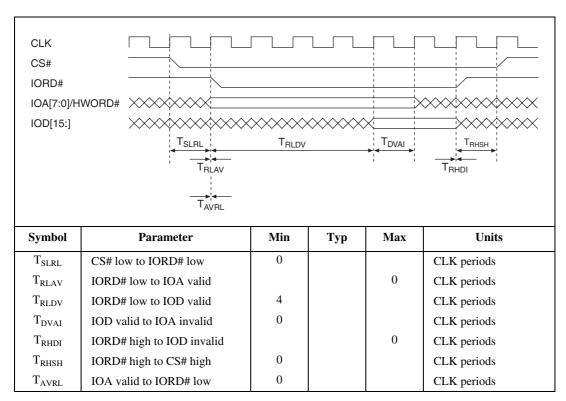

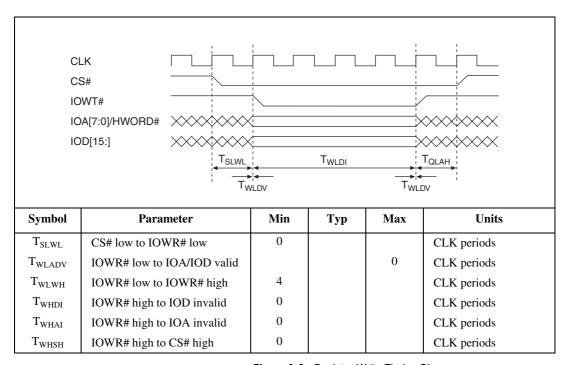

Appendix A

Electrical Specifications and Timing

Appendix B

Mechanical Information

Appendix C GPIB Remote Messages

Appendix D

Technical Support and Professional Services

## **About This Manual**

The TNT5002 is high performance GPIB interface that supports the following two modes of usage (refer to Chapter 1, *Architectural Overview*, for a complete description of different modes):

- PCI4882 mode—In this mode, the TNT5002 is able to run all NI-488.2 based drivers developed for the PCI-GPIB unmodified. This mode is functionally equivalent to One-chip mode in the NI TNT4882 with a PCI interface. This is the default mode for the TNT5002.

- GEN4882 mode—In this mode, the TNT5002 is functionally equivalent to One-chip mode in the NI TNT4882/TNT4882C. Any application written for the TNT4882/TNT4882C in mode will run unmodified on the TNT5002.

The TNT5002 implements *IEEE 488.1* Interface Functions SH1, AH1, T5, TE5, L3, LE3, SR1, RL1, PP1, PP2, DC1, and DT1. The TNT5002 also implements HS488 Interface Functions AHE1, SHE1, and CF1.

The TNT5002 implements Controller function C0, allowing no Controller capability in any mode.

A DMA Controller with a 64-byte FIFO may be used in PCI4882 mode. This may be used in addition to the 32-byte GPIB FIFO, effectively making a 96-byte FIFO.

The TNT5002 also implements *IEEE 488.1* Electrical Driver/Receiver Capability E2 (three-state drivers).

### **Product Features**

- Complies with PCI Local Bus Specification, Revision 2.1 or 2.2

- Complies with *IEEE 488.1 Standard Digital Interface for Programmable Instrumentation* and *IEEE 488.2*

- Complete backwards compatibility with software written using NI-488.2, NI-488DDK, or NI-Device

- Complies with HS488<sup>1</sup>

<sup>&</sup>lt;sup>1</sup> Assuming PCI4882 or GEN4882 modes

- PCI Bus-master<sup>1</sup>

- Auto-negotiating handshake, can use HS488 capable instruments and non-HS488 instruments simultaneously<sup>1</sup>

- Automatic GPIB EOS and/or NL remote message detection

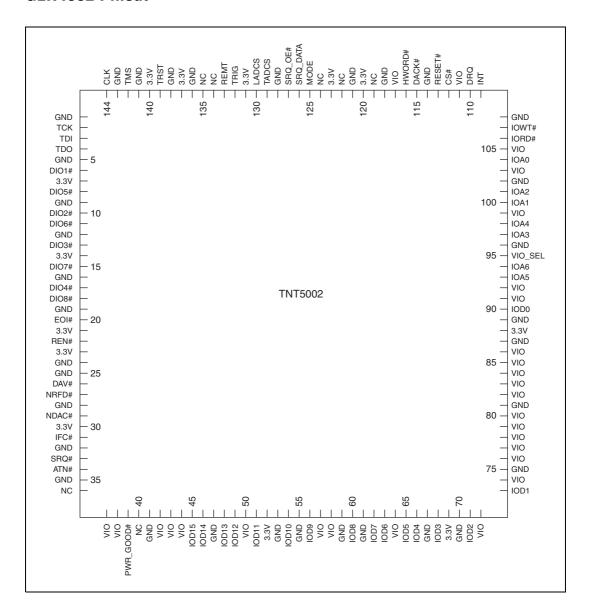

- 144-pin PQFP package or 256 Fine-pitch BGA package

- 3.3V core

- 3.3V or 5V PCI/Generic interface signaling environments

- Integrated *IEEE 488.1* compliant three-state GPIB transceivers

- Can use PCI clock or external 40 MHz clock for GPIB circuitry (40 MHz external clock required for maximum transfer rates and all HS488 transfers)

- 32-bit PCI or 16-bit generic interface

- 64-byte PCI DMA FIFO<sup>1</sup>

- 32-byte GPIB FIFO<sup>1</sup>

- Transfer rates up to 8 Mbytes/s using HS488<sup>1</sup>

- Transfer rates up to 1.5 Mbytes/s using *IEEE 488.1* handshake

- TNT5002 performs the following *IEEE 488.1* Interface Functions: SH1, AH1, T5, TE5, L3, LE3, SR1, RL1, PP1, PP2, DC1, DT1, C0

- TNT5002 performs HS488 Functions AHE1, SHE1, and CF1<sup>1</sup>

- NI TNT4882 One-chip compatible register set

- Indicator pins: REM, talk addressed, listen addressed

- Synchronous design

#### **How To Use This Manual**

This manual is designed for use in two ways. Chapter 3, *Register Descriptions*, contains a listing of registers sorted first by group and then alphabetically. Chapter 4, *Functional Description—PCI4882 and GEN4882 Modes*, contains different sections addressing different GPIB concepts, such as parallel polling and GPIB data transfers.

Users who are very familiar with the register set may find Chapter 3, *Register Descriptions*, easier to use because specific registers are easy to find. Users who are less familiar may find Chapter 4, *Functional Description—PCI4882 and GEN4882 Modes*, easier because all of the

<sup>&</sup>lt;sup>1</sup> Assuming PCI4882 mode

register bits needed to perform a certain GPIB function are often located in different registers.

#### **Conventions**

The following conventions appear in this manual:

The » symbol leads you through nested menu items and dialog box options to a final action. The sequence **File**»**Page Setup**»**Options** directs you to pull down the **File** menu, select the **Page Setup** item, and select **Options**

from the last dialog box.

# The pound sign indicates a signal is active low. Active low signals are

logically asserted when in a low state; such as a pin being grounded or a

register bit being 0.

+ The plus symbol is a logical binary OR operator.

& The ampersand symbol is a logical binary AND operator.

~ The tilde is a logical unary negation operator.

\* The asterisk is the multiplication operator.

This icon denotes a note, which alerts you to important information.

active-low Active-low means that the signal should be at a logic low state to be

asserted. For example, RST# is an active-low signal that resets various internal registers. The registers are reset when RST# is at logic 0 (ground).

byte 8 bits

DMA is an acronym for Direct Memory Access. In the TNT5002, DMA is

used to transfer data automatically between system memory and the GPIB FIFO. During DMA transfers, a DMA controller initiates register accesses.

dword 32 bits

IEEE 488.2

IEEE 488.1 and IEEE 488.1 and IEEE 488.2 refer to the ANSI/IEEE Standard 488.1-1987

and the ANSI/IEEE Standard 488.2-1992, respectively, which define the

GPIB.

italic Italic text denotes variables, emphasis, a cross reference, or an introduction

to a key concept. This font also denotes text that is a placeholder for a word

or value that you must supply.

monospace

Text in this font denotes text or characters that you should enter from the keyboard, sections of code, programming examples, and syntax examples. This font is also used for the proper names of disk drives, paths, directories, programs, subprograms, subroutines, device names, functions, operations, variables, filenames and extensions, and code excerpts.

word 16 bits

#### **Mnemonic Conventions**

There are many mnemonics that appear in this manual. Some mnemonics are spelled identically but may differ in case; some are all capitalized and some are all lower case. The following guidelines describe the naming convention used:

| Convention                                                                                                                                                                       | Examples                           |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|

| Register mnemonics are capitalized.                                                                                                                                              | CHOR, CFG, PCIDR                   |

| Register bit mnemonics are capitalized.                                                                                                                                          | ADSR[LPAS],<br>DCR[BERHAND]        |

| Register bit mnemonics are prefixed by the register in which they are accessed, except when they are used in the bit descriptions of the registers in which the bit is accessed. | CHSR[ERROR],<br>CFG[CCEN]          |

| A mnemonic for a register bit may refer to a bit in more than one register. This is clarified by prefixing a bit mnemonic with the register in which the bit is accessed.        | CHSR[INT],<br>ISR3[INT]            |

| Similar bits in a given register may be grouped together and indexed with brackets.                                                                                              | PPR[LPPE[3:0]],<br>CHCR[SWAP[1:0]] |

| One bit of a group of similar bits in a given register may be indexed without brackets.                                                                                          | PPR[LPPE2],<br>CHCR[SWAP0]         |

| Signal pins are capitalized.                                                                                                                                                     | FRAME#, DAV#, SCL                  |

| GPIB local messages as defined in <i>IEEE 488.1</i> are lower case.                                                                                                              | rdy, nba                           |

| GPIB remote messages as defined in <i>IEEE 488.1</i> are capitalized.                                                                                                            | TCT, DCL                           |

| All GPIB signal pin names are suffixed with #.                                                                                                                                   | DAV#, NRFD#                        |

| All AUXCR, AUXMR, and CMDR commands are capitalized.                                                                                                                             | IFC, ~IST                          |

| Convention                                                                                        | Examples   |

|---------------------------------------------------------------------------------------------------|------------|

| All IEEE 488.1 state machine state names are capitalized.                                         | SDYS, CIDS |

| The indexing brackets may be left off a bus name if the entire bus is the subject of the context. | DIO#, AD   |

#### **Related Documentation**

The following documents contain information that you might find helpful as you read this manual:

- ANSI/IEEE Standard 488.1-1987, IEEE Standard Digital Interface for Programmable Instrumentation

- ANSI/IEEE Standard 488.2-1992, IEEE Standard Codes, Formats, Protocols, and Common Commands

# **Architectural Overview**

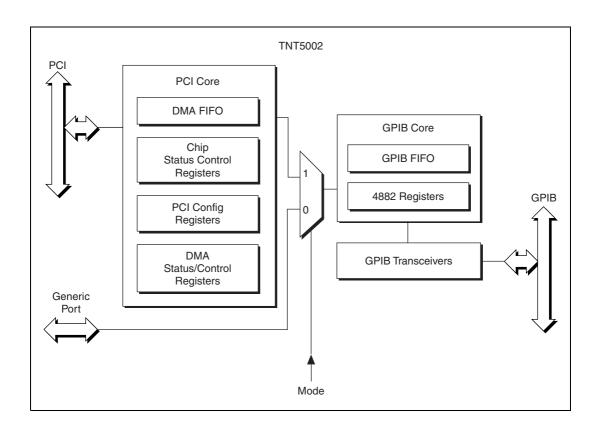

# TNT5002 Block Diagram

#### **TNT5002 Mode Selection**

There are two distinct modes of operation in the TNT5002. PCI4882 and GEN4882 modes implement the TNT4882 One-chip register set. This register set can be accessed through a generic IO interface or a PCI interface. PCI4882 mode implements a PCI bus-master interface. GEN4882 mode implements a generic IO interface. The two different modes of operation are outlined in the following table. The interface must be selected by the MODE pin and must not be changed dynamically since the pinout is significantly different between interfaces.

|         | User Configuration |                  | TNT5002 Features        |           |                                |

|---------|--------------------|------------------|-------------------------|-----------|--------------------------------|

| Mode    | MODE<br>Pin        | Reset Command    | GPIB<br>Register<br>Set | Interface | Total FIFO<br>Depth<br>(Bytes) |

| PCI4882 | 3.3V               | CMDR[SOFT_RESET] | 4882                    | PCI       | 64 + 32                        |

| GEN4882 | GND                | CMDR[SOFT_RESET] | 4882                    | Generic   | 32                             |

### FIFO Overview

If the TNT5002 is in PCI4882 mode, there are two FIFOs: a 32-byte FIFO connected to the GPIB and a 64-byte FIFO connected to the PCI bus.

The 32-byte GPIB FIFO (GFIFO) is used for both GPIB reads and writes. It can be written to and read from simultaneously by the DMA Controller and Source/Acceptor GPIB state machines.

The 64-byte DMA FIFO (DFIFO) connected to the PCI bus is used for DMA transfers. This FIFO is connected to the PCI bus on one side and the GFIFO on the other side.

During DMA transfers, bytes are automatically transferred between the DFIFO and GFIFO. The GFIFO should never be directly accessed. The TNT5002 always interprets all DMA accesses between the GFIFO and DMA FIFO as 16-bit operations. During programmed IO (PIO) operations, the DMA FIFO is never accessed, just the GFIFO.

If the TNT5002 is in GEN4882 mode, there is one 32-byte FIFO connected to the GPIB. This FIFO can be accessed through either PIO or DMA.

### **DMA Overview**

If the TNT5002 is in PCI4882 mode, the DMA Controller must be used to maximize transfer rates. The GPIB registers in the TNT5002 are configured in the same manner regardless of whether DMA is used. If DMA is used, the GPIB FIFO should not be directly accessed because the DMA Controller automatically transfers data between the DMA FIFO and GPIB FIFO.

If the TNT5002 is in GEN4882 mode, an external DMA controller can be connected to the TNT5002.

# **Signal Pins**

# **Signal Definitions and Conventions**

| Type | Definition                                                                                                                                                                        |  |  |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| I    | Standard input only.                                                                                                                                                              |  |  |

| О    | Standard output only.                                                                                                                                                             |  |  |

| TS   | Tristate bi-directional.                                                                                                                                                          |  |  |

| STS  | Sustained tristate. Active low signal must be pulled high for one cycle when deasserting.                                                                                         |  |  |

| OD   | Standard open drain.                                                                                                                                                              |  |  |

| PU   | Signal is pulled up internally with a 25 k $\Omega$ -100 k $\Omega$ resistor. Although these pins are pulled up internally, they should also be connected to either 3.3V or GND.  |  |  |

| PD   | Signal is pulled down internally with a 30 k $\Omega$ –90 k $\Omega$ resistor. Although these pins are pulled up internally, they should also be connected to either 3.3V or GND. |  |  |

| GT   | GPIB Transceiver.                                                                                                                                                                 |  |  |

# **GPIB Signals**

The following 16 signals implement the GPIB protocol as described in *IEEE 488.1*. These signals exist in all modes.

#### **GPIB Data Signals**

| Pin Name  | Туре | Description                                                                                                                                                                                                                                                                             |

|-----------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DIO#[8:1] | GT   | Data Lines—The eight DIO lines carry command and data messages on the GPIB. All commands and most data bytes use the 7-bit ASCII or ISO code set, leaving the eighth bit, DIO8#, unused or used for parity. However, applications may use DIO8# as a normal data signal for 8-bit data. |

#### **GPIB Interface Management Signals**

These signals are used for signaling among controllers and devices.

| Pin Name | Type | Description                                                                                                                                                    |

|----------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IFC#     | GT   | Interface Clear—The System Controller asserts IFC# to place all devices into a known quiescent state.                                                          |

| ATN#     | GT   | Attention—The Controller-in-Charge asserts ATN# when it sends commands and unasserts ATN# when it sends data messages.                                         |

| SRQ#     | GT   | <b>Service Request</b> —A device asserts SRQ# to request service from a Controller.                                                                            |

| REN#     | GT   | Remote Enable—The System Controller asserts REN# to enable devices for remote programming.                                                                     |

| EOI#     | GT   | End or Identify—A Talker asserts EOI# to signal the end of data. EOI# is also asserted by the Controller-in-Charge to signal the execution of a parallel poll. |

## **GPIB Handshake Signals**

These signals are used to handshake data and command bytes using both 3-wire and HS488 transfer protocols.

| Pin Name | Type | Description                                                                                                                                                                                                                                                                          |

|----------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DAV#     | GT   | Data Valid—DAV# indicates whether DIO# is stable and whether devices can safely accept the signals. When a Controller sends commands, it controls DAV#, and when a Talker sends data it controls DAV#.                                                                               |

| NRFD#    | GT   | Not Ready for Data—NRFD# indicates whether a Listener is ready to receive a data byte. NRFD# is driven by all active Listeners when a Talker is sending data or by all devices when the Controller is sending commands. NRFD# is also used by the Talker to control HS488 transfers. |

| NDAC#    | GT   | Not Data Accepted—NDAC# indicates whether all devices have accepted the byte for which DAV# was most recently asserted. NDAC# is driven by all active Listeners when a Talker is sending data or by all devices when a Controller is sending commands.                               |

# **Device Signals**

# Miscellaneous Signals (All Modes)

| Pin Name | Туре  | Description                                                                                                                                                                                                                                                                                            |

|----------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| EXT_CLK  | I     | GPIB Circuitry Clock—This clock may be used for the GPIB circuitry. It should be driven by an external oscillator at 40MHz. In PCI4882 or PCI9914 modes this pin must remain undriven if USE_PCI_CLK is asserted because the GPIB circuitry will be clocked by PCI_CLK.                                |

| TRIGGER  | O     | Trigger—The trigger pin is asserted when the DT state machine is in DTAS. DTAS is entered after receiving the Group Execute Trigger (GET) command as an Addressed Listener, or after writing AUXMR[TRIG]. TRIGGER unasserts after either leaving DTAS or three clock cycles after writing AUXMR[TRIG]. |

| SRQ_OE#  | I, PU | <b>SRQ# Output Enable</b> —This debugging pin asynchronously enables the SRQ# transceiver when asserted. The logic state is then determined by SRQ_DATA. This pin must be unasserted for normal operation.                                                                                             |

| SRQ_DATA | I, PU | SRQ# Data Input—When SRQ_OE# is asserted this debugging pin determines the drive state of the SRQ# transceiver. Asserting this pin causes the SRQ# transceiver to drive SRQ# actively false. Unasserting this pin causes the SRQ# transceiver to drive SRQ# actively true.                             |

### Miscellaneous Signals (PCI4882 Mode)

| Pin Name    | Туре   | Description                                                                                                                                                                                                                |  |

|-------------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| USE_ROM     | I, PU  | Use Serial Rom—This pin determines if the TNT5002 loads a PCI Device ID and serial number from the serial ROM. If this pin is asserted, serial autoload occurs. If this pin is unasserted, serial autoload does not occur. |  |

| SCL         | О      | Serial ROM Clock Pin—This clock is generated by the TNT5002 and connected to the clock input of a serial ROM. The frequency of this clock is approximately 65 kHz when PCI_CLK is 33 MHz.                                  |  |

| SDA         | TS, PU | <b>Serial ROM Data Pin</b> —This bidirectional data pin is the serial data line between the TNT5002 and serial ROM. This pin is an output when writing to the serial ROM and an input when reading from the serial ROM.    |  |

| DIS_SUBSYS  | I, PU  | <b>Disable PCI SUBSYSTEM ID</b> —If this pin is asserted, reading the PCI SUBSYSTEM ID returns 0x000000000. If this pin is actively driven low, reading the PCI SUBSYSTEM ID register returns the same value as the PIDR.  |  |

| USE_PCI_CLK | I      | Use PCI Clock—When this pin is asserted, the GPIB circuitry is clocked by the PCI_CLK. If this pin is unasserted, the GPIB circuitry is clocked by EXT_CLK.                                                                |  |

#### **Indicator Signals**

These pins indicate various states of the GPIB state machines. These are general purpose outputs and can be used to drive an LED, for example. These signals exist in all modes.

| Pin Name | Туре | Description                                                                                                                               |  |

|----------|------|-------------------------------------------------------------------------------------------------------------------------------------------|--|

| LADCS    | 0    | Active Listener—This pin asserts when the Listener state machine is in LADS or LACS. This pin reflects the state of ADSR[LA].             |  |

| TADCS    | 0    | Active Talker—This pin asserts when the Talker state machine is in TADS, TACS, or SPAS. This pin reflects the state of ADSR[LA].          |  |

| REMT     | 0    | <b>Remote Enabled</b> —This pin asserts when the Remote/Local state machine is in REMS or RWLS. This pin reflects the state of ISR2[REM]. |  |

# **PCI Signals**

These signals implement a PCI interface. These signals only exist in PCI4882 mode. In GEN4882 mode, these pins have different functionality.

| Pin Name   | Type | Description                                                                                                                                                                                                                                                                                                                               |  |

|------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| PCI_CLK    | I    | PCI Clock—This is the clock input from the PCI bus.                                                                                                                                                                                                                                                                                       |  |

| AD[31:0]   | TS   | PCI Address/Data—These signals are the multiplexed PCI address and data bus.                                                                                                                                                                                                                                                              |  |

| C/BE#[3:0] | TS   | Command/Byte Enable—These signals are the multiplexed command and byte enables. During the PCI address phase C/BE# conveys the type of transfer taking place. Following the address phase, C/BE# indicates whether valid data is present on the four byte lanes of the AD bus.                                                            |  |

| PAR        | TS   | Parity—PAR carries the even parity over the AD and C/BE# buses during address and data phases. The device that drives AD and CBE# also drives PAR. PAR is valid one clock cycle after AD and C/BE# are valid.                                                                                                                             |  |

| FRAME#     | STS  | <b>Frame</b> —A PCI master asserts FRAME# to indicate the beginning and duration of a transaction. FRAME# assertion indicates the beginning of a PCI transaction. Data transactions can continue while FRAME# is asserted. FRAME# unassertion indicates the final data phase requested by the initiator.                                  |  |

| IRDY#      | STS  | Initiator Ready—IRDY# is driven by the initiator of a transaction to indicate the initiator's ability to complete the current data phase. During a write transaction, IRDY# is asserted when valid data is driven onto the AD bus. During a read, IRDY# is asserted when the initiator is able to accept data for the current data phase. |  |

| TRDY#      | STS  | Target Ready—TRDY# is driven be the target of a transaction to indicate the target's ability to complete the current data phase. During a write transaction, TRDY# is asserted when the target is able to accept data for the current data phase. During a read, TRDY# is asserted when the target is driving valid data onto the AD bus. |  |

| Pin Name | Туре | Description                                                                                                                                                                                                                                                            |  |

|----------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| DEVSEL#  | STS  | <b>Device Select</b> —DEVSEL# is asserted by the target to indicate that the device is accepting the transaction.                                                                                                                                                      |  |

| STOP#    | STS  | <b>Stop</b> —This signal is driven by the target to request that the initiator stop the current transaction.                                                                                                                                                           |  |

| IDSEL#   | STS  | <b>Initialization Device Select</b> —This signal is used as the chip select for Type 0 PCI configuration accesses to PCI configuration space.                                                                                                                          |  |

| PERR#    | STS  | <b>Parity Error</b> —PERR# is asserted when a parity error is detected. PERR# can be asserted by the target during a write transaction and by the initiator during a read transaction.                                                                                 |  |

| SERR#    | TS   | <b>System Error</b> —SERR# is asserted to indicate a serious system problem or a parity error during the address phase of a data transfer.                                                                                                                             |  |

| REQ#     | TS   | Bus Request—REQ# is asserted to request access to the bus.                                                                                                                                                                                                             |  |

| GNT#     | I    | Bus Grant—GNT# is asserted to grant access to the bus.                                                                                                                                                                                                                 |  |

| INTA#    | TS   | Interrupt—This signal is asynchronously asserted to interrupt the CPU.                                                                                                                                                                                                 |  |

| PCI_RST# | I    | PCI Reset—This signal is used to initialize the device to a known state. While PCI_RST# is asserted all PCI and GPIB signals are tri-stated. PCI_RST# must be asserted during power-up to ensure that the GPIB signals do not glitch when connected to another device. |  |

# **Generic Interface Signals**

These signals implement a generic bus interface. These signals only exist in GEN4882 mode. In PCI4882 mode, these pins have different functionality.

| Pin Name  | Туре | Description                                                                                                                                                                                                    |  |

|-----------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| DACK#     | I    | DMA Acknowledge—DACK#, along with IORD# or IOWT#, asserts during DMA accesses.                                                                                                                                 |  |

| CS#       | I    | Chip Select—CS#, along with IORD# or IOWT#, asserts during IO accesses.                                                                                                                                        |  |

| DRQ       | О    | <b>DMA Request</b> —DRQ is asserted to request a DMA transfer.                                                                                                                                                 |  |

| HWORD#    | I    | <b>16-Bit Access</b> —HWORD# is asserted during 16-bit register accesses and unasserted for 8-bit register accesses. HWORD# is ignored during DMA accesses.                                                    |  |

| INT       | TS   | Interrupt—INT asserts when an enabled interrupt condition is true.                                                                                                                                             |  |

| IOA[6:0]  | I    | Address—IOA selects a register during IO accesses.                                                                                                                                                             |  |

| IOD[15:0] | Ю    | <b>Data</b> —IOD is the 16-bit bi-directional data bus used for DMA and IO accesses. During 8-bit writes data must be on the lower 8 bits. During 8-bit reads the data will be smeared across both byte lanes. |  |

| IORD#     | I    | Read—IORD# is asserted to indicate an IO or DMA read.                                                                                                                                                          |  |

| IOWT#     | I    | Write—IOWT# is asserted to indicate an IO or DMA write.                                                                                                                                                        |  |

| RESET#    | I    | Reset—RESET# resets the chip to its initial power-on state. RESET# also asynchronously tri-states the GPIB transceivers.                                                                                       |  |

# **Power/Ground Pins**

The location of power and ground pins are the same among all modes, although the meaning of the pins changes slightly.

#### **PCI4882 Power/Ground Pins**

The following pins supply power to the TNT5002 in PCI4882 mode.

| Pin Name | Description                                                                                                                                                                                                                                                                                                                                                                                                  |  |

|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 3.3V     | Core/GPIB Transceiver Power—These pins provide power for the digital core and all output signal pins except PCI signals. These pins must be connected to a 3.3V source. If not connected directly to the PCI 3.3V power rail, the 3.3V supply they are connected to cannot vary by more than 170mV. If these pins are connected to the PCI 3.3V rail, that rail may vary according to the PCI Specification. |  |

| VIO      | <b>PCI Transceiver Power</b> —These pins provide power for the PCI Transceivers. These must be connected to 3.3V or 5V as allowed by the PCI Specification.                                                                                                                                                                                                                                                  |  |

| GND      | <b>Ground</b> —These pins are ground pins for both power inputs.                                                                                                                                                                                                                                                                                                                                             |  |

| VIO_SEL  | <b>VIO Comparator</b> —This input is used to determine whether VIO is 3.3V or 5V. This signal is compared against 3.3V and must be directly connected to VIO.                                                                                                                                                                                                                                                |  |

#### **GEN4882 Power/Ground Pins**

The following pins supply power to the TNT5002 in GEN4882 mode.

| Pin Name | Description                                                                                                                                                                                                                                      |

|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3.3V     | <b>Core/GPIB Transceiver Power</b> —These pins provide power for the digital core and all output signal pins except the Generic Interface signals. These pins must be connected to a 3.3V source.                                                |

| VIO      | Generic Interface Transceiver Power—These pins provide power for the Generic Interface Transceivers. The generic interface pins can be powered from either 3.3V or 5V. The voltage connected to VIO is used to drive the generic interface pins. |

| GND      | Ground—These pins are ground pins for both power inputs.                                                                                                                                                                                         |

| Pin Name  | Description                                                                                                                                                         |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VIO_SEL   | <b>VIO Comparator</b> —This input is used to determine whether VIO is 3.3V or 5V. This signal is compared against 3.3V and must be directly connected to VIO.       |

| PWR_GOOD# | <b>Power Good</b> —This input must be asserted while 3.3V is out of the specified operating range. For example, this pin must be asserted while 3.3V is ramping up. |

# **Register Descriptions**

# **Register Groups**

The following tables group the registers into functional blocks such that all registers in a given block serve a similar function.

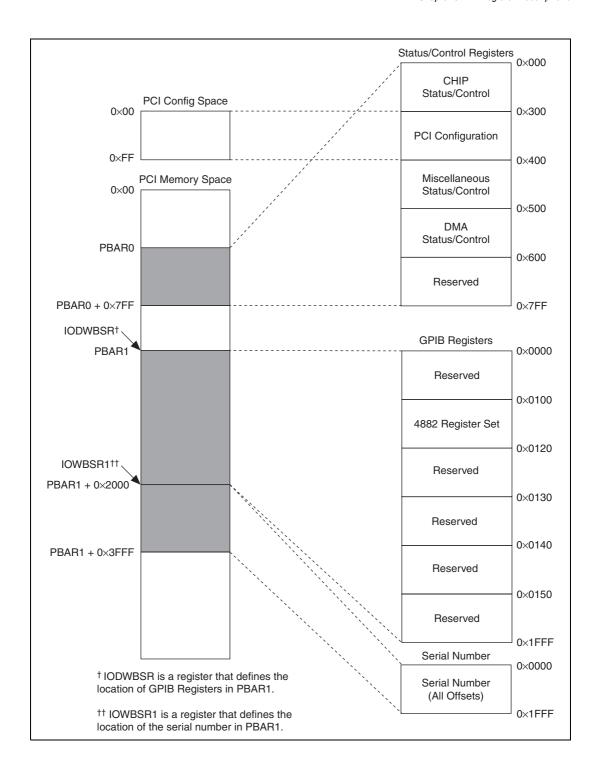

### Register Groups in PCI4882 Mode

| Offset from PBAR0 | Register Group               |  |

|-------------------|------------------------------|--|

| 0x000-0x2FF       | Chip Status/Control          |  |

| 0x300-0x3FF       | PCI Configuration            |  |

| 0x400-0x4FF       | Miscellaneous Status/Control |  |

| 0x500-0x5FF       | DMA Status/Control           |  |

| 0x600-0x7FF       | Reserved                     |  |

| Offset from PBAR1 | Register Group    |  |

|-------------------|-------------------|--|

| 0x0000-0x00FF     | Reserved          |  |

| 0x0100-0x011F     | 4882 Register Set |  |

| 0x0120-0x012F     | Reserved          |  |

| 0x0130-0x013F     | Reserved          |  |

| 0x0140-0x014F     | Reserved          |  |

| 0x0150-0x1FFF     | Reserved          |  |

| 0x2000-0x3FFF     | Serial Number     |  |

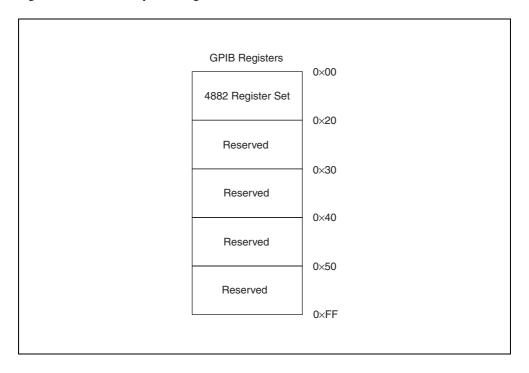

## Register Groups in GEN4882 Mode

| Offset    | Register Group    |  |

|-----------|-------------------|--|

| 0x00-0x1F | 4882 Register Set |  |

| 0x20-0x2F | Reserved          |  |

| 0x30-0x3F | Reserved          |  |

| 0x40-0x4F | GPIB Test/Status  |  |

| 0x50-0x7F | Reserved          |  |

# PCI4882 Mode Register Map

# **GEN4882 Mode Register Map**

The following register map is valid when interfacing through generic interface. These registers are accessed by asserting CS# or DACK# and IORD# or IOWR#.

# **TNT5002 Status/Control Register Group**

These registers are only available in PCI4882 mode. This register group is used to control and configure the PCI interface.

#### TNT5002 Status/Control Registers Sorted by Offset

Registers at offsets not listed are reserved.

| Offset<br>from PBAR0 | Mnemonic | Write Register             | Read Register                |

|----------------------|----------|----------------------------|------------------------------|

| 0x14                 | LCISR2   | Reserved                   | Local CPU Interrupt Status 2 |

| 0xC0                 | IODWBSR  | IO Device Window Base/Size | IO Device Window Base/Size   |

| 0xC4                 | IOWBSR1  | IO Window 1 Base/Size      | IO Window 1 Base/Size        |

## TNT5002 Status/Control Registers Sorted by Mnemonic

Registers at offsets not listed are reserved.

| Mnemonic | Offset<br>from PBAR0 | Write Register             | Read Register                |

|----------|----------------------|----------------------------|------------------------------|

| IODWBSR  | 0xC0                 | IO Device Window Base/Size | IO Device Window Base/Size   |

| IOWBSR1  | 0xC4                 | IO Window 1 Base/Size      | IO Window 1 Base/Size        |

| LCISR2   | 0x14                 | Reserved                   | Local CPU Interrupt Status 2 |

### **TNT5002 Status/Control Register Descriptions**

### 10 Device Window Base Size Register (IODWBSR)

| Offset 0xC0 from PBAR0 |     |       | Res | Reset Value: 0x00000000 |    |    |    |

|------------------------|-----|-------|-----|-------------------------|----|----|----|

| BA[31:24]              |     |       |     |                         |    |    |    |

| 31                     | 30  | 29    | 28  | 27                      | 26 | 25 | 24 |

| BA[23:16]              |     |       |     |                         |    |    |    |

| 23                     | 22  | 21    | 20  | 19                      | 18 | 17 | 16 |

|                        | B[1 | 5:12] |     | R                       | R  | R  | R  |

| 15                     | 14  | 13    | 12  | 11                      | 10 | 9  | 8  |

| WIENA D                |     |       |     |                         |    |    |    |

| WENAB                  | R   | R     | R   | R                       | R  | R  | R  |

| 7                      | 6   | 5     | 4   | 3                       | 2  | 1  | 0  |

The IODWBSR determines the address of the GPIB registers. This register must be written with PBAR1 + 0x00000080 to access the GPIB registers.

| Mnemonic  | Type | Description                                                                                                                    |

|-----------|------|--------------------------------------------------------------------------------------------------------------------------------|

| BA[31:12] | R/W  | <b>Base Address</b> —The base address of the GPIB registers in PCI address space. These bits are only valid when WENAB is set. |

| WENAB     | R/W  | Window Enable—If this bit is set, the Window is enabled. If this bit is clear the window is disabled.                          |

| R         | R/W  | <b>Reserved</b> —Always write 0 to these bits. These bits are read as either 0 or 1.                                           |

### IO Window Base/Size Register 1 (IOWBSR1)

| Offset 0xC4 f | set 0xC4 from PBAR0 |    |      |        | Reset Value: 0x00000000 Read/Wi |    |    |  |

|---------------|---------------------|----|------|--------|---------------------------------|----|----|--|

|               |                     |    | BA[3 | 1:24]  |                                 |    |    |  |

| 31            | 30                  | 29 | 28   | 27     | 26                              | 25 | 24 |  |

|               |                     |    | BA[2 | 23:16] |                                 |    |    |  |

| 23            | 22                  | 21 | 20   | 19     | 18                              | 17 | 16 |  |

|               |                     |    | BA[  | 15:8]  |                                 |    |    |  |

| 15            | 14                  | 13 | 12   | 11     | 10                              | 9  | 8  |  |

| WENAD         | D.                  | D. |      |        | WCIZE(4.01                      |    |    |  |

| WENAB         | R                   | R  |      |        | WSIZE[4:0]                      |    |    |  |

| 7             | 6                   | 5  | 4    | 3      | 2                               | 1  | 0  |  |

The IODWBSR determines the address of the serial number. This register must be written with PBAR1 + 0x0000208C to access the serial number.

| Mnemonic   | Type | Description                                                                                                                                                                                              |

|------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BA[31:8]   | R/W  | <b>Base Address</b> —The base address in PCI address space. The number of bits compared is determined by the WSIZE[4:0].                                                                                 |

| WENAB      | R/W  | Window Enable—If this bit is set, the Window is enabled. If this bit is clear the window is disabled.                                                                                                    |

| WSIZE[4:0] | R/W  | Window Size—These bits determine the size of the serial number window in PBAR1. The size in bytes is 2 <sup>(WSIZE + 1)</sup> . WSIZE should be set to 01100, indicating the size of the window is 8 kB. |

| R          | R/W  | <b>Reserved</b> —Always write 0 to these bits. These bits are read as either 0 or 1.                                                                                                                     |

| Offset 0x14 f | rom PBAR0 |    |    | Rese | et Value: 0x00 | 0000000 | Read Only |

|---------------|-----------|----|----|------|----------------|---------|-----------|

| PCIINT        | R         | R  | R  | R    | R              | R       | R         |

| 31            | 30        | 29 | 28 | 27   | 26             | 25      | 24        |

| R             | R         | R  | R  | R    | R              | R       | R         |

| 23            | 22        | 21 | 20 | 19   | 18             | 17      | 16        |

| R             | R         | R  | R  | R    | R              | R       | R         |

| 15            | 14        | 13 | 12 | 11   | 10             | 9       | 8         |

| R             | R         | R  | R  | R    | R              | R       | R         |

| 7             | 6         | 5  | 4  | 3    | 2              | 1       | 0         |

This register reflects various interrupts. This register should not be accessed for most applications.

| Mnemonic | Type | Description                                                                          |  |  |  |

|----------|------|--------------------------------------------------------------------------------------|--|--|--|

| PCIINT   | R    | PCI Interrupt—PCIINT is ISR3[INT].                                                   |  |  |  |

| R        | R    | <b>Reserved</b> —Always write 0 to these bits. These bits are read as either 0 or 1. |  |  |  |

# **PCI Configuration Registers**

These registers are only available in PCI4882 mode.

#### **PCI Configuration Register Map**

All PCI devices must support a set of configuration registers that control the behavior of the PCI device and provide a consistent location for a PCI device to indicate its status. The PCI specification does support some functionality that is superfluous to the requirements of the TNT5002's PCI interface. The register space, as implemented in the PCI interface, is shown in the following table.

|          | Offset in           | 0.00                      | Byte 3                               | Byte 2   | 2             | Byte 1           | Byte 0          |  |

|----------|---------------------|---------------------------|--------------------------------------|----------|---------------|------------------|-----------------|--|

| Mnemonic | PCI Config<br>Space | Offset in<br>Memory Space | 31 24                                | 23       | 16            | 15 8             | 7 0             |  |

| PIDR     | 0x00                | PBAR0 + 0x300             | Devi                                 | ce ID    |               | Vend             | Vendor ID       |  |

| PSCR     | 0x04                | PBAR0 + 0x304             | PCI S                                | Status   |               | PCI (            | CI Control      |  |

| PCCRIDR  | 0x08                | PBAR0 + 0x308             |                                      | Class Co | ode           |                  | Revision ID     |  |

| PLIVR    | 0x0C                | PBAR0 + 0x30C             | (                                    | )        |               | Latency Timer    | Cache Line Size |  |

| PBAR0    | 0x10                | PBAR0 + 0x310             |                                      | Base     | Addre         | ess Register 0   |                 |  |

| PBAR1    | 0x14                | PBAR0 + 0x314             |                                      | Base     | Addre         | ess Register 1   |                 |  |

| Reserved | 0x18                | PBAR0 + 0x318             | Reserved                             |          |               |                  |                 |  |

| Reserved | 0x1C                | PBAR0 + 0x31C             | Reserved                             |          |               |                  |                 |  |

| Reserved | 0x20                | PBAR0 + 0x320             | Reserved                             |          |               |                  |                 |  |

| Reserved | 0x24                | PBAR0 + 0x324             | Reserved                             |          |               |                  |                 |  |

| PCISR    | 0x28                | PBAR0 + 0x328             |                                      | Reserve  | d/CIS         | Pointer Register |                 |  |

| PSUBR    | 0x2C                | PBAR0 + 0x32C             | Subsystem ID Subsystem Ve            |          | Vendor ID     |                  |                 |  |

| Reserved | 0x30                | PBAR0 + 0x330             | Reserved                             |          |               |                  |                 |  |

| Reserved | 0x34                | PBAR0 + 0x334             | Reserved                             |          |               |                  |                 |  |

| Reserved | 0x38                | PBAR0 + 0x338             | Reserved                             |          |               |                  |                 |  |

| PLRIDR   | 0x3C                | PBAR0 + 0x33C             | Max_Lat Min_Gnt                      |          | Interrupt Pin | Interrupt Line   |                 |  |

| PBACOR   | 0x40                | PBAR0 + 0x340             | Base Address Configuration Register  |          |               | er               |                 |  |

| Reserved | 0x44                | PBAR0 + 0x344             | Reserved                             |          |               |                  |                 |  |

| PERCR    | 0x48                | PBAR0 + 0x348             | Expansion ROM Configuration Register |          |               |                  | ter             |  |

### **PCI Configuration Register Descriptions**

### **Device ID/Vendor ID Register (PIDR)**

| Offset 0x00 fr | rom PCI Con     | fig Space, 0x3 | 00 from PBA | R0 Res    | et Value: See | Description | Read Only |  |

|----------------|-----------------|----------------|-------------|-----------|---------------|-------------|-----------|--|

|                | DEVICE_ID[15:8] |                |             |           |               |             |           |  |

| 31             | 30              | 29             | 28          | 27        | 26            | 25          | 24        |  |

|                |                 |                | DEVICE      | _ID[7:0]  |               |             |           |  |

| 23             | 22              | 21             | 20          | 19        | 18            | 17          | 16        |  |

|                | VENDOR_ID[15:8] |                |             |           |               |             |           |  |

| 15             | 14              | 13             | 12          | 11        | 10            | 9           | 8         |  |

|                |                 |                |             |           |               |             |           |  |

|                |                 |                | VENDO       | R_ID[7:0] |               |             |           |  |

| 7              | 6               | 5              | 4           | 3         | 2             | 1           | 0         |  |

| Mnemonic        | Type | Description                                                                                                                                                                          |

|-----------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DEVICE_ID[15:0] | R    | <b>Device Identification Number</b> —The default DEVICE_ID of the TNT5002 is 0xC850. The default DEVICE_ID is overwritten from a serial ROM if USE_ROM is asserted or not connected. |

| VENDOR_ID[15:0] | R    | <b>Vendor Identification Number</b> —This sixteen bit value is assigned by the PCI Special Interest Group. National Instruments' PCI Vendor ID number is 0x1093.                     |

### **PCI Status and Control Register (PSCR)**

| Offset 0x04 fr | rom PCI Conf | fig Space, 0x3 | 04 from PBA | R0 Res | et Value: 0x02 | 2000000 | Read/Write |

|----------------|--------------|----------------|-------------|--------|----------------|---------|------------|

| PERRDT         | SERRDT       | SMABT          | RTABT       | STABT  | SPEEDA         | SPEEDB  | PARDT      |

| 31             | 30           | 29             | 28          | 27     | 26             | 25      | 24         |

| FBBC           | 0            | 0              | 0           | 0      | 0              | 0       | 0          |

| 23             | 22           | 21             | 20          | 19     | 18             | 17      | 16         |

| 0              | 0            | 0              | 0           | 0      | 0              | 0       | SERREN     |

| 15             | 14           | 13             | 12          | 11     | 10             | 9       | 8          |

| ADSTEP         | PERREN       | 0              | MWIEN       | 0      | MSTREN         | MEMEN   | IOEN       |

| 7              | 6            | 5              | 4           | 3      | 2              | 1       | 0          |

Bits 31–16 are status bits. The PCI interface sets the bits in these registers. In order to clear a bit in the status register, a PCI device must write a one to the bit. This convention is required by the PCI specification. Bits 15–0 are control bits, and these bits are read/write.

| Mnemonic | Type | Description                                                                                                                                       |

|----------|------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| PERRDT   | R/W  | Parity Error Detect—This bit is set when the PCI interface detects a parity error even when parity error handling is disabled by clearing PERREN. |

| SERRDT   | R/W  | <b>System Error Detected</b> —The PCI interface sets this bit when it asserts SERR#.                                                              |

| SMABT    | R/W  | <b>Signal Master Abort</b> —The PCI interface sets this bit if it terminates a PCI master cycle with a master abort.                              |

| RTABT    | R/W  | Receive Target Abort—The PCI interface sets this bit to indicate that it received a target abort while performing a PCI master cycle.             |

| STABT    | R/W  | <b>Signal Target Abort</b> —The PCI interface sets this bit if it terminates a slave cycle with a target abort.                                   |

| Mnemonic         | Туре | Description                                                                                                                                                                                                                                                |

|------------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SPEEDA<br>SPEEDB | R/W  | Address Decoding Speed—SPEEDA and SPEEDB are hardwired to 0 and 1, respectively, to indicate that the PCI interface is a medium speed decoder. These bits are set in accordance with the PCI specification requirements. Writes to these bits are ignored. |

| PARDT            | R/W  | Parity Detect—The PCI interface sets this bit if three conditions are met:                                                                                                                                                                                 |

|                  |      | The PCI interface asserted PERR# or detected that PERR# was asserted by another device.                                                                                                                                                                    |

|                  |      | The PCI interface was performing a master cycle when PERR# was asserted.                                                                                                                                                                                   |

|                  |      | PERREN is set.                                                                                                                                                                                                                                             |

| FBBC             | R/W  | Fast Back-to-Back Capable—This bit is hardwired to 1 indicating that the PCI interface supports fast back-to-back transfers as a PCI slave. Writes to this bit are ignored.                                                                                |

| SERREN           | R/W  | SERR# Enable—Setting this bit permits the PCI interface to assert SERR# during system error conditions. Clearing this bit prevents the PCI interface from asserting SERR#.                                                                                 |

| ADSTEP           | R/W  | <b>Address Stepping</b> —This bit is hardwired to 0 to indicate that address or data stepping is not performed. Writes to this bit are ignored.                                                                                                            |

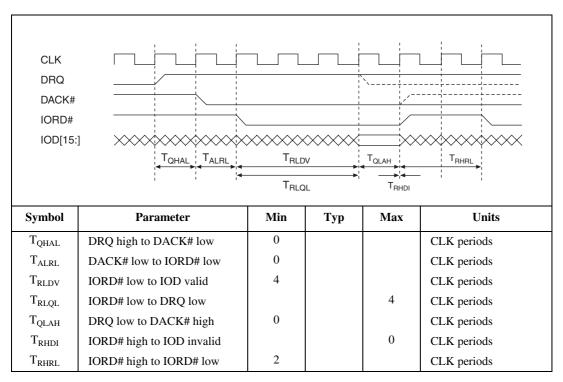

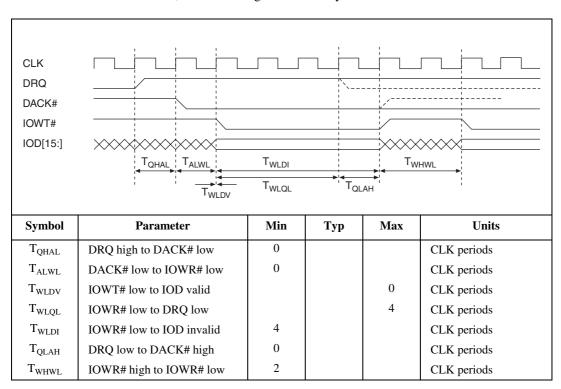

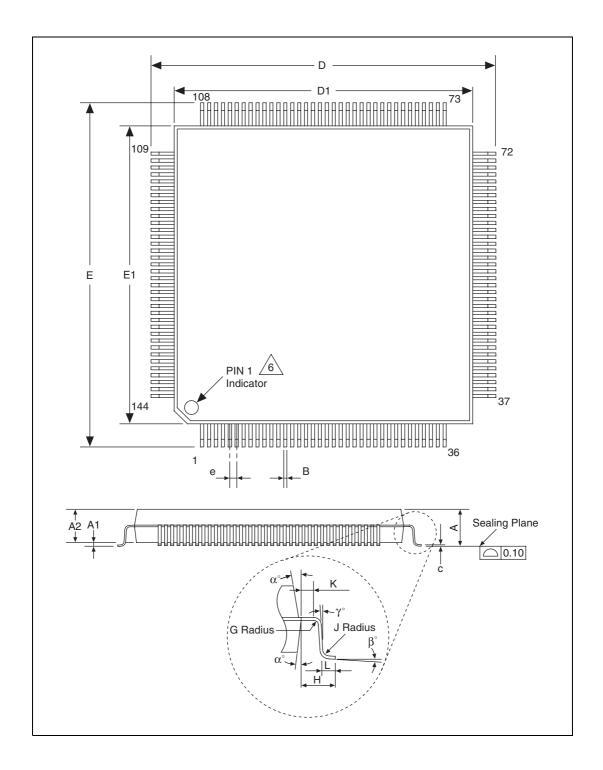

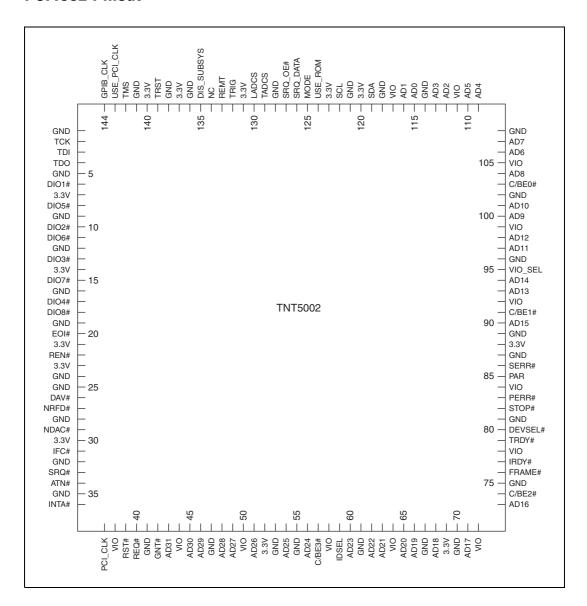

| PERREN           | R/W  | Parity Error Response Enable—Setting this bit enables the PCI interface to assert PERR# and set PERRDT. If this bit is cleared, the PCI interface must ignore parity errors and continue normal operations.                                                |